# SCORING INDICATORS (VERSION B)

### COURSE NAME: MICROCONTROLLER &PLC

COURSE CODE: 6031C

QID:2102240043

| Q No | Scoring Indicators                                                                                                                                                         | Split<br>score | Sub<br>Total | Total<br>Score |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------|----------------|

|      | PART A                                                                                                                                                                     |                |              | 9              |

| I. 1 | No of I/O Ports = 4                                                                                                                                                        | 1              | 1            |                |

| I. 2 | IE (Interrupt Enable) Register, IP (Interrupt Priority) Register  ( any one)                                                                                               | 1              | 1            |                |

| I. 3 | PUSH<br>POP                                                                                                                                                                | 0.5*2          | 1            |                |

| I. 4 | CLR A                                                                                                                                                                      | 1              | 1            |                |

| I. 5 | Disadvantages of PLC  1. There's too much work required in connecting wires.  2. There's difficulty with changes or replacements.  3. It's always difficult to find errors | 0.5*2          | 1            |                |

|      | 4. It requires a skillful workforce.  5. When a problem occurs, hold-up time is indefinite, usually long.  (write any two)                                                 |                |              |                |

| I. 6 | Lights, Alarms Actuators Solenoid Valves Contactors, Motors Relays  (write any two)                                                                                        | 0.5*2          | 1            |                |

Page 1 of 24

| I.7  | Industrial Applications of PLC                                                                                                  | 0.5*2 | 1   |

|------|---------------------------------------------------------------------------------------------------------------------------------|-------|-----|

|      | The Transportation System likes Conveyor Belt System.                                                                           |       |     |

|      | <ul> <li>Packing and Labeling System in Food &amp;<br/>Beverage.</li> </ul>                                                     |       |     |

|      | <ul> <li>Automatic Bottle or Liquid Filling System.</li> <li>Packaging and Labeling System in Pharma<br/>Industries.</li> </ul> |       |     |

|      | (any two applications)                                                                                                          |       |     |

| . 8  | Power rails                                                                                                                     | 1     | 1   |

|      |                                                                                                                                 |       | 100 |

| 1. 9 | 1 Outsut -                                                                                                                      | 1     | 1   |

| Q No  |          | S      | coring | g Indica           | itors   |    |           | Split<br>score | Sub<br>Total | Total<br>Score |

|-------|----------|--------|--------|--------------------|---------|----|-----------|----------------|--------------|----------------|

|       |          |        | PA     | RT B               |         |    |           |                |              | 30             |

| II. 1 | MSB      |        |        |                    |         |    | LSB       | 3              | 3            |                |

|       | GATE C/T | M1     | MO     | GATE               | C/T     | M1 | MO        |                |              |                |

|       | • Gate   | /Count | er onl | s set to<br>y when | 1, it E |    | Γ1 pin is |                |              |                |

Page 2 of 24

|       | C                                   | ounter or if it i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | is equal to one then it acts as a is 0 then it act as a timer.  les the mode of the timer  Bit format-2 label-1                                                                    |     |   |

|-------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|

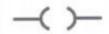

| II. 2 | (See app                            | endix for bloc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | k diagram of 8051)                                                                                                                                                                 | 3   | 3 |

| II. 3 | 5 Interno. 1. E 2. T 3. E 4. T 5. S | upts in 8051 n<br>upts in 8051 (<br>xternal hardwa<br>imer 0 overflo<br>xternal hardwa<br>imer 1 overflo<br>erial interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ents that interrupts the normal nicrocontroller  with order of normal priority)  are interrupts <u>INTO</u> ow interrupt TO  are interrupts <u>INT1</u> ow interrupt T1  (TI & RI) | 3   | 3 |

|       | non mas                             | kable . When                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | timate interrupt in 8051 and is ever a high level is applied to ers a reset condition  Definition -1 Listing-2                                                                     |     |   |

| II. 4 | non mas<br>RST pin                  | kable . When                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ever a high level is applied to ers a reset condition  Definition -1  Listing-2                                                                                                    | 1*3 | 3 |

| П. 4  | non mas<br>RST pin                  | kable . When<br>the 8051 ente                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ever a high level is applied to ers a reset condition  Definition -1  Listing-2                                                                                                    | 1*3 | 3 |

| П. 4  | non mas<br>RST pin                  | kable . When the solution the solution to the solution of the solution of the solution of the solution that the solution is solution to the solution of the solution that the solution is solution to the solution that the solution is solution to the solution that th | ever a high level is applied to ers a reset condition  Definition -1 Listing-2  port 3 pins                                                                                        | 1*3 | 3 |

| П. 4  | Alternat                            | the 8051 enters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Definition -1 Listing-2  Description                                                                                                                                               | 1*3 | 3 |

| П. 4  | Alternate P3 bit P3.0               | e functions of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Definition -1 Listing-2  Description  Description  Serial Data Reception                                                                                                           | 1*3 | 3 |

| II. 4 | Alternate P3 bit P3.0 P3.1          | the 8051 enterest the 8051 ent | Definition -1 Listing-2  Tport 3 pins  Description  Serial Data Reception  Serial Data Transmission                                                                                | 1*3 | 3 |

| П. 4  | Alternate P3 bit P3.0 P3.1 P3.2     | the 8051 enterest the 8051 ent | Definition -1 Listing-2  Description  Serial Data Reception  External Interrupt 0                                                                                                  | 1*3 | 3 |

| II. 4 | P3 bit P3.0 P3.1 P3.2 P3.3          | table . When the soft enter the soft | Definition -1 Listing-2  Description  Description  Serial Data Reception  Serial Interrupt 0  External Interrupt 1                                                                 | 1*3 | 3 |

|       | P3.7                                                                 | <u>RD</u>                                                                 | Read Signal                                                                                                                                                                                                                                           |                               |   |

|-------|----------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---|

| II. 5 | the value of Eg:- if [A]  XCH A, R  SWAP -in order nibb  Eg: if [A]= | eontained in<br>=30H and R<br>6; [A]=45<br>terchanges 1<br>les(bit 7 to 4 | value of the Accumulator was register/Memory location.  6=[45]H, after  H and [R6]=30H  lower order(bit 3 to 0) and high of the accumulator.                                                                                                          |                               | 3 |

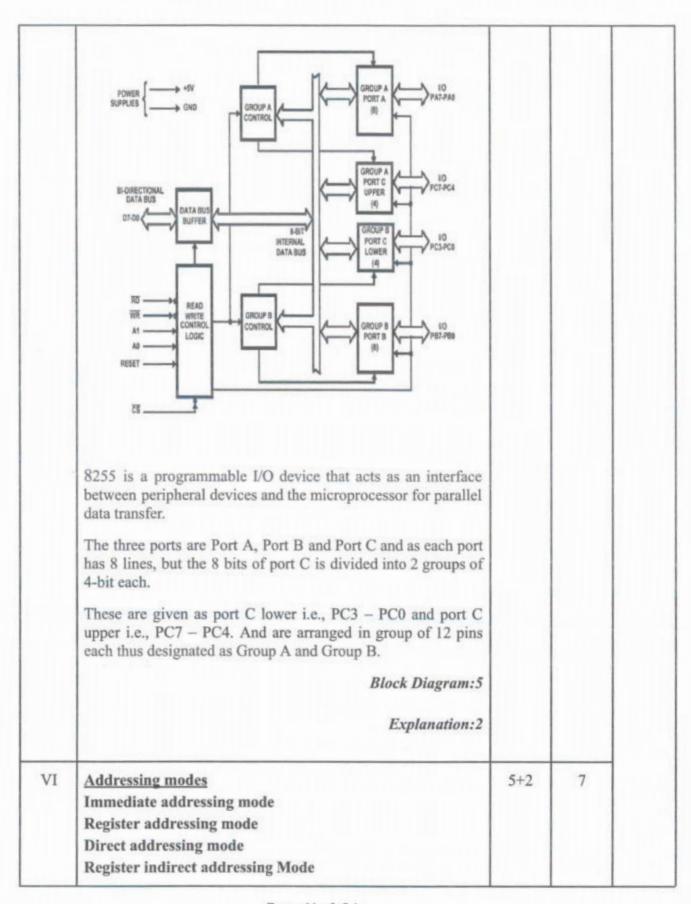

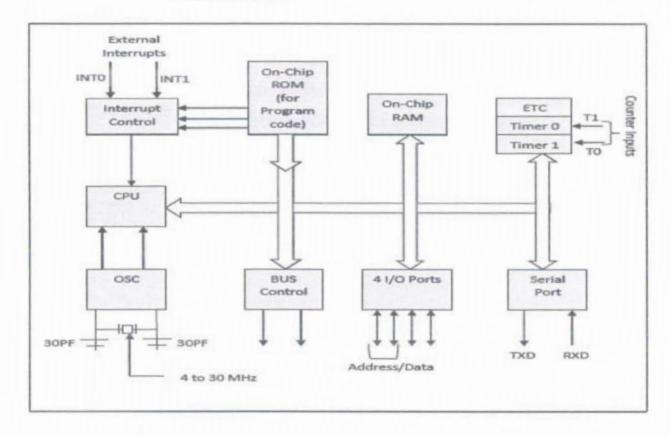

| II. 6 | Control Vinterface (See appear                                       |                                                                           | 255 programmable periphe                                                                                                                                                                                                                              | eral 3                        | 3 |

| П.7   | mark)  Prode Ar (P) sys Pro                                          | occessor Movice chitecture:PLC) was destems ogrammable ecified by         | odule: Single microprocest rogrammable Logic Control signed to replace the relay-base Logic Controllers are generally available of input available of input available of power supply -ac/dc mming language language -There languages for PLC include | ssor<br>llers<br>ased<br>ally | 3 |

| (Write any six features)                                                                            |   |   |

|-----------------------------------------------------------------------------------------------------|---|---|

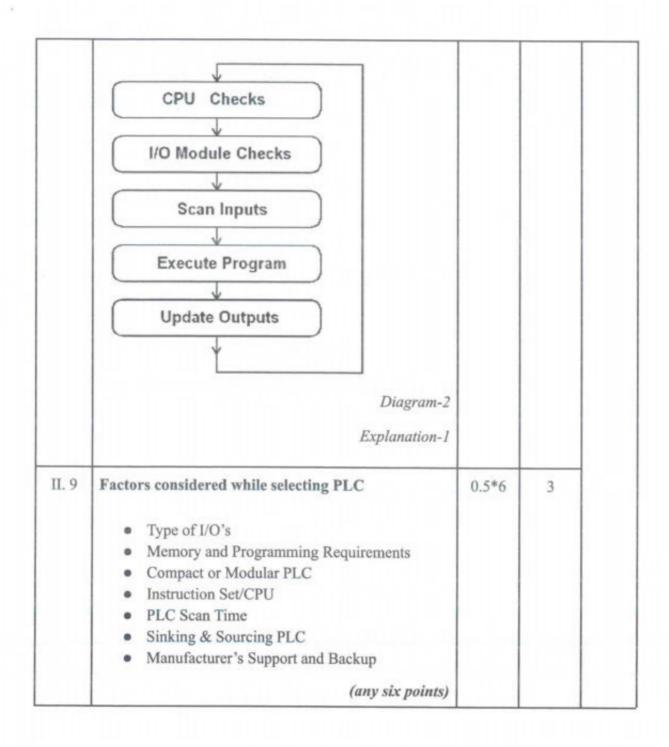

| . 8 Operation of PLC                                                                                | 3 | 3 |

| PLCs operate by continually scanning programs and repeat this process many times per second.        |   |   |

| When a PLC starts, it runs checks on the hardware and software for faults, also called a self-test. |   |   |

| If there are no problems, then the PLC will start the scan cycle.                                   |   |   |

| The scan cycle consists of three steps: input scan, executing program(s), and output scan.          |   |   |

| Input Scan: PLC reads the status of the inputs and solves the logic.                                |   |   |

| Execute Program (or Logic Execution): The PLC executes a program one instruction at a time          |   |   |

| Output Scan: When the ladder scan completes, the PLC updates the status of the outputs              |   |   |

| Q No | Scoring Indicators                                                                                                                                                                                                                                                                                                                                                                                                   | Split<br>score | Sub<br>Total | Total<br>Score |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------|----------------|

|      | PART C                                                                                                                                                                                                                                                                                                                                                                                                               |                |              | 84             |

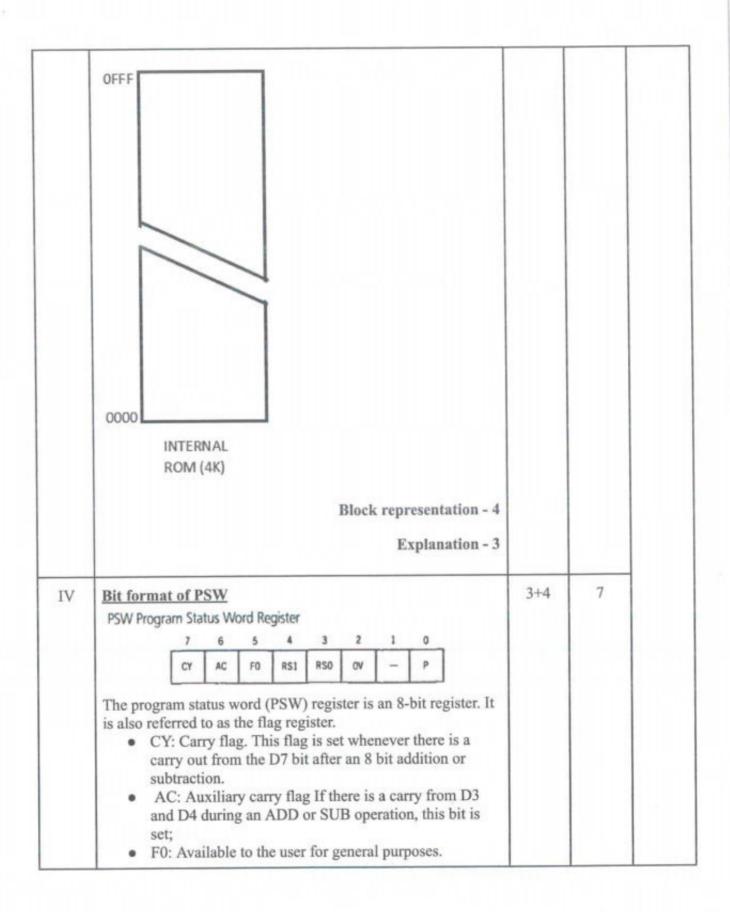

| Ш    | Internal memory organisation of 8051 microcontroller                                                                                                                                                                                                                                                                                                                                                                 | 4+3            | 7            |                |

|      | Internal Data Memory (RAM)  The Data Memory or RAM of the 8051 Microcontroller stores temporary data and intermediate results that are generated and used during the normal operation of the microcontroller, the 8051 Microcontroller have 128B of RAM, i.e., memory addresses from 00H to 7FH and are divided into Working Registers (organized as Register Banks), Bit – Addressable Area and General Purpose RAM |                |              |                |

In the first 128B of RAM (from 00H to 7FH), the first 32B i.e., memory from addresses 00H to 1FH consists of 32 Working Registers that are organized as four banks with 8 Registers in each Bank.

Internal programme memory (ROM)

Program Memory (ROM) is used for a permanent saving program being executed, In 8051 Microcontroller, the code or instructions to be executed are stored in the Program Memory, which is also called as the ROM of the Microcontroller. The original 8051 Microcontroller by Intel has 4KB of internal ROM.

| inte      | rnal RAM                                                                 |                                                                          |     |   |

|-----------|--------------------------------------------------------------------------|--------------------------------------------------------------------------|-----|---|

| RS1       | RS0                                                                      | Reg Bank<br>Selected                                                     |     |   |

| 0         | 0                                                                        | Bank 0                                                                   |     |   |

| 0         | 1                                                                        | Bank 1                                                                   |     |   |

| 1         | 0                                                                        | Bank 2                                                                   |     |   |

| 1         | 1                                                                        | Bank 3                                                                   |     |   |

| of a high | signed number operation order bit to overflow arity flag The parity flag | ag reflects the number of 1s ister only. If the A register 1s, then P=1. |     |   |

|           |                                                                          | structure - 3<br>explanation - 4                                         |     |   |

|           |                                                                          |                                                                          | 5+2 | 7 |

Indexed addressing mode Implied Addressing Mode

#### Immediate addressing mode:

The data is provided in the instruction itself. The data is provided immediately after the opcode.

Example:

MOV R3, #45H; move data #45H to R3

#### Register addressing mode:

The source and the destination both are registers, and must be of the same size. The data transfer can take place between Rn (n=0 to 7) registers and the Accumulator (A) only and cannot be done between Rn registers.

Example:

MOV A, R5; move contents of R5 to Accumulator

#### Direct addressing mode:

The source or destination address is specified by using 8-bit data in the instruction. Only the internal data memory can be used in this mode.

Example:

MOV 80H, R6; move contents of R6 to RAM Location 80H

MOV R2, 45H; move contents of RAM location 45H to register R2

#### Register indirect addressing Mode

In this mode, the source or destination address is given in the register. By using register indirect addressing mode, the internal or external addresses can be accessed. Example:

MOV A, @R0H; move contents of RAM location whose address is held by R0 into A

|   | Indexed add                                                                                                        | dressing n                                    | node                    |                 |             |                                              |     |   |

|---|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------|-----------------|-------------|----------------------------------------------|-----|---|

|   | Indexed add<br>by adding ar<br>The offset is<br>addressing r<br>registers.<br>Examples:-<br>MOVC A, @<br>MOVC A, @ | offset to<br>is usually<br>mode of 8<br>A+PC; | a base add<br>stored in | ress.<br>one of | the regist  | ers.Index                                    | ed  |   |

|   | Implied Add<br>In the implied<br>These types<br>These types<br>instructions.<br>Examples:-<br>RL A;                | ed address<br>of instruc<br>of instruc        | ing mode,<br>tion can w | ork on s        | pecific reg | gisters on                                   | ly. |   |

|   |                                                                                                                    |                                               |                         |                 | Ex          | (any thre<br>Listing<br>planation<br>Example | -1  |   |

| П | Assembly lan                                                                                                       |                                               |                         | dd R0 an        | d R1 and st |                                              | 7   | 7 |

|   |                                                                                                                    | ORG 4                                         | 000                     |                 |             |                                              |     |   |

|   | 4000                                                                                                               | MOV A                                         |                         |                 | py 1st No.  |                                              |     |   |

|   | HERE:                                                                                                              | MOVX                                          | @DPTR, #2500<br>@DPTR,A |                 | Save Sum    |                                              |     |   |

|   | Accumulator                                                                                                        | END<br>=                                      |                         |                 |             |                                              |     |   |

|   |                                                                                                                    | _                                             | T                       |                 |             |                                              | 1   |   |

|      | Carry flag = 0 |                                         |                                                          |                                  |                                                              |     |   |

|------|----------------|-----------------------------------------|----------------------------------------------------------|----------------------------------|--------------------------------------------------------------|-----|---|

| VIII |                |                                         |                                                          |                                  |                                                              | 1*7 | 7 |

|      | MO             | V A, #5AH                               | [A]=5A                                                   |                                  |                                                              |     |   |

|      | RR             | A                                       | [A]=2D                                                   |                                  |                                                              |     |   |

|      | SWA            | AP A                                    | [A]=D2                                                   |                                  |                                                              |     |   |

|      | CLR            | R C                                     | CY=0                                                     |                                  |                                                              |     |   |

|      | RRC            | CA                                      | [A]=69                                                   | CY=0                             |                                                              |     |   |

|      | CPL            | A                                       | [A]=96                                                   |                                  |                                                              |     |   |

|      | RL             | A                                       | [A]=2D                                                   |                                  |                                                              |     |   |

| 137  |                |                                         | -                                                        |                                  |                                                              |     | _ |

| IX   |                |                                         |                                                          |                                  |                                                              | 1*7 | 7 |

|      |                | PLC                                     |                                                          | Relay                            |                                                              |     |   |

|      | 1)Basic        | logic by u                              | controller<br>ms software<br>sing input &<br>dules, CPU, | electro-m<br>switching<br>device | is an<br>nechanical<br>g hardware<br>(Hardware<br>g Device)  |     |   |

|      | 2)Function     | as well as                              | monitoring<br>s controlling<br>designing                 | controlling<br>the<br>circuit.   | only a<br>ng role in<br>designing<br>Monitoring<br>easy with |     |   |

|      | 3) Working:    | 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 | ing                                                      |                                  | we cannot<br>program.                                        |     |   |

| 4) Design:       | Easily modify the designing circuit.                  | Modification of the electronic circuit is more difficult as compared to PLC |     |   |

|------------------|-------------------------------------------------------|-----------------------------------------------------------------------------|-----|---|

| 5)Memory         | consist of memory to store programme                  | no memory                                                                   |     |   |

| 6) I/O           | It has more capabilities of input and output modules. | The relay does not have more capabilities.                                  |     |   |

| 7)<br>Operation: | PLC is operated on the digital system.                | It is operated on the analog system.                                        |     |   |

|                  |                                                       |                                                                             |     |   |

| Block diagra     | m of PLC                                              |                                                                             | 4+3 | 7 |

| Input Device     | Power Supply  Central Input Processing Ou             | Output Device                                                               | 4+3 | 7 |

|                  | Power Supply  Central Processing Out                  |                                                                             | 4+3 | 7 |

| Input and output module: The input between input devices and central production which is used to convert analog signal in the output module is a mediator between the central processing unit (CPU) which into analog signal.  Power supply: power supply is provided. | processing unit (CPU)<br>nto digital signal.<br>en output devices and<br>a converts digital signal |      |   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------|---|

| input and output module unit. Power su or separately mounted unit.                                                                                                                                                                                                     |                                                                                                    |      |   |

| Memory section: The memory section in which data and information is stored                                                                                                                                                                                             |                                                                                                    |      |   |

| Programming device: Programming devices used for loading the user programmemory or edit it and to monitor the exof the PLC.                                                                                                                                            | am into the program                                                                                |      |   |

|                                                                                                                                                                                                                                                                        | Block diagram: 4                                                                                   |      |   |

| 1                                                                                                                                                                                                                                                                      |                                                                                                    |      |   |

|                                                                                                                                                                                                                                                                        | Explanation: 3                                                                                     |      |   |

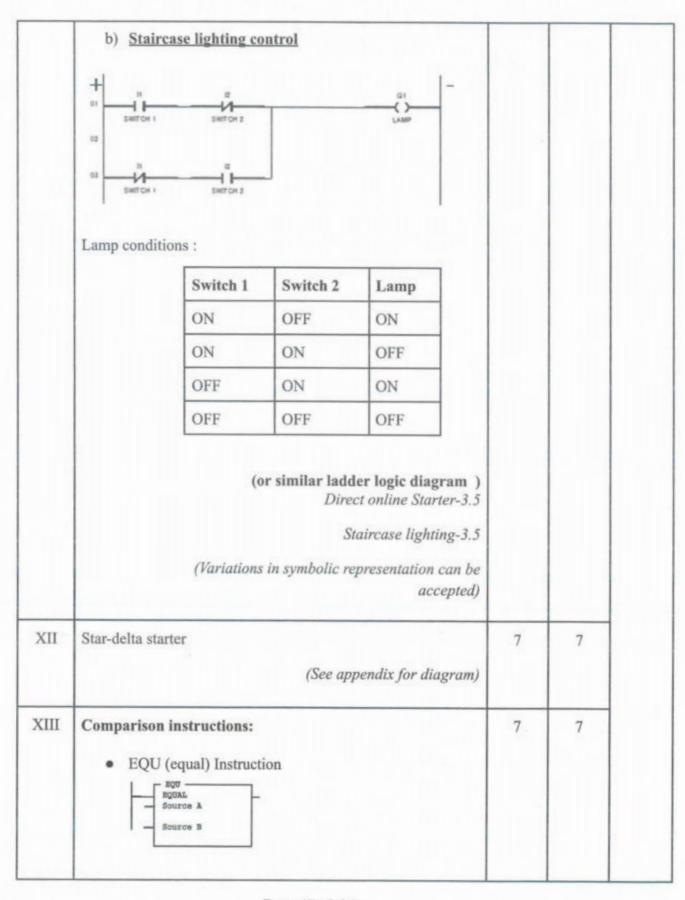

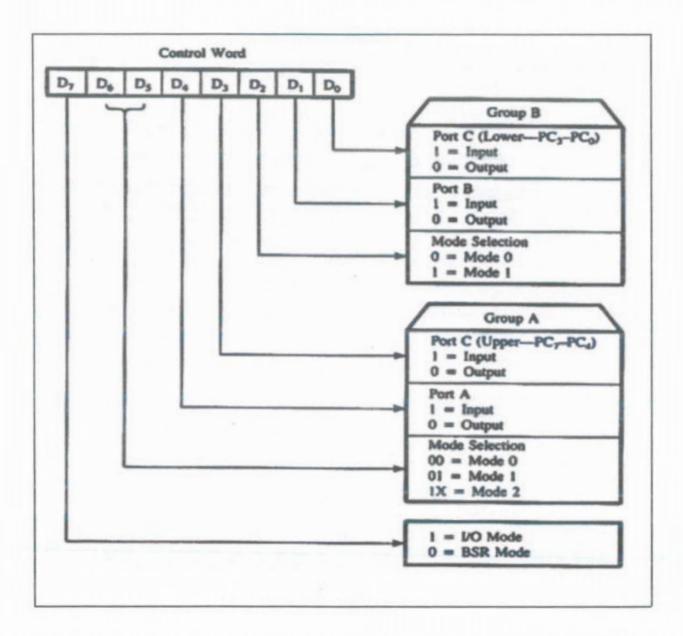

| a) <u>Direct online Starter</u>                                                                                                                                                                                                                                        | Explanation: 3                                                                                     | 3.5+ | 7 |

| a) Direct online Starter   t                                                                                                                                                                                                                                           | a:                                                                                                 | 3.5+ | 7 |

| 5TART STOP OU                                                                                                                                                                                                                                                          | a:                                                                                                 |      | 7 |

| Inputs:  START- To start the motor- NO STOP - To stop the motor-NC                                                                                                                                                                                                     | a:                                                                                                 |      | 7 |

| Inputs:  START- To start the motor- NO                                                                                                                                                                                                                                 | a:                                                                                                 |      | 7 |

Page 17 of 24

Use the EQU instruction to test whether two values are equal. If source A and source B are equal, the instruction is logically true.

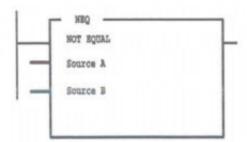

· NEQ (not equal) Instruction

Use the NEQ instruction to test whether two values are not equal. If source A and source B are not equal, the instruction is logically true.

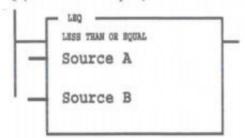

· LEQ (Less than or equal) Instruction

Use the LEQ instruction to test whether one value (source A) is less than or equal to another (source B). If the value at source A is less than or equal to the value at source B, the instruction is logically true.

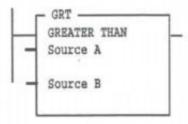

GRT(Greater than) Instruction

Use the GRT instruction to test whether one value

| (source A) is greater than another (source B). If the value at source A is greater than the value at source B, the instruction is logically true.  • GEQ(Greater than or equal) Instruction  GEQ GRTR THAN OR EQUAL Source A  Source B  Use the GEQ instruction to test whether one value (source A) is greater than or equal to another (source B). If the value at source A is greater than or equal to the value at source B, the instruction is logically true.  (any 4 comparison instructions)  (Variations in symbolic representation can be |   |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|

| (i) Normally open contact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7 | 7 |

| The NO (Normally open)instruction looks and operates like a normally open relay contact. There is a memory bit associated with each NO instruction that is linked to the status of an input device or internal condition.  If the input device is ON or Closed, then the corresponding bit                                                                                                                                                                                                                                                          |   |   |

The NC(Normally closed) instruction looks and operates like a normally closed relay contact. There is a memory bit associated with each NC instruction that is linked to the status of an input device or internal condition.

If the input device is OFF or Open, then the corresponding bit in the data memory is set to 1, thus allowing the current to flow from its left side to its right-hand side. Otherwise, it is set to 0, thus blocking the current.

#### (iii) OFF delay timer

A off-delay (TOF) timer is a PLC programming instruction which use to switch off the output or system after a certain amount of time.

#### (iv) Output relay coil

If the condition of the left link of the output relay coil is ON then the corresponding bit in the output data memory is set. The device wired to this output is also energized.

# **Appendix**

# Part B

# II.2 Schematic block diagram of 8051

ladder logic or similar